VLSI Design

Module Aims

•

Introduction to VLSI Technology

–

Process

Design

•

Trends

•

Chip

Fabrication

•

Real

Circuit Parameters

–

Circuit

Design

•

Electrical

Characteristics

•

Configuration

Building Blocks

•

Switching

Circuitry

•

Translation

onto Silicon

•

CAD

–

Practical

Experience in Layout Design

Learning

Outcomes

•

Understand the principles of the design

and implementation of standard MOS integrated circuits and be able to assess

their performance taking into account the effects of real circuit parameters

Laboratory

•

Micro wind layout and simulation package

•

Dedicated to training in sub-micron CMOS

VLSI design

•

Layout editor, electrical circuit

extractor and on-line analogue simulator

Reading

List

Why VLSI?

•

Integration

improves the design

–

Lower

parasitic = higher speed

–

Lower

power consumption

–

Physically

smaller

•

Integration

reduces manufacturing cost - (almost) no manual assembly

Module

1

Introduction

to VLSI Technology

•

Introduction

•

Typical Applications

•

Moore’s Law

•

The cost of fabrication

•

Technology Background

•

What is a chip

•

Switches

•

Doping

•

IC Technology

•

Basic MOS Transistor

•

Fabrication Technology

•

CMOS Technology

•

BiCMOS

VLSI Applications

•

VLSI

is an implementation technology for electronic circuitry - analogue or digital

•

It

is concerned with forming a pattern of interconnected switches and gates on the

surface of a crystal of semiconductor

•

Microprocessors

–

personal

computers

–

microcontrollers

•

Memory

- DRAM / SRAM

•

Special

Purpose Processors - ASICS (CD players, DSP applications)

•

Optical

Switches

•

Has

made highly sophisticated control systems mass-producible and therefore cheap

Moore’s Law

•

Gordon

Moore: co-founder of Intel

•

Predicted

that the number of transistors per chip would grow exponentially (double every

18 months)

•

Exponential

improvement in technology is a natural trend:

–

e.g.

Steam Engines - Dynamo - Automobile

The Cost of Fabrication

•

Current

cost $2 - 3 billion

•

Typical

fab line occupies 1 city block, employees a few hundred employees

•

Most

profitable period is first 18 months to 2 years

•

For

large volume IC’s packaging and testing is largest cost

•

For

low volume IC’s, design costs may swamp manufacturing costs

Technology Background

What is a Silicon Chip?

•

A

pattern of interconnected switches and gates on the surface of a crystal of

semiconductor (typically Si)

•

These

switches and gates are made of

–

areas

of n-type silicon

–

areas

of p-type silicon

–

areas

of insulator

–

lines

of conductor (interconnects) joining areas together

•

Aluminium,

Copper, Titanium, Molybdenum, polysilicon, tungsten

•

The geometry of these areas is known as the

layout of the chip

•

Connections

from the chip to the outside world are made around the edge of the chip to

facilitate connections to other devices

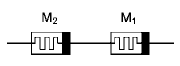

Switches

•

Digital equipment is largely composed of

switches

•

Switches can be built from many

technologies

–

relays (from which the earliest

computers were built)

–

thermionic valves

–

transistors

•

The perfect digital switch would have

the following:

–

switch instantly

–

use no power

–

have an infinite resistance when off and

zero resistance when on

•

Real switches are not like this!

Semiconductors

and Doping

•

Adding trace amounts of certain

materials to semiconductors alters the crystal structure and can change their

electrical properties

–

in particular it can change the number

of free electrons or holes

•

N-Type

–

semiconductor has free electrons

–

dopant is (typically) phosphorus,

arsenic, antimony

•

P-Type

–

semiconductor has free holes

–

dopant is (typically) boron, indium,

gallium

Dopants are usually implanted into the semiconductor

using Implant Technology, followed by thermal process to diffuse the dopants

IC

Technology

•

Speed / Power performance of available

technologies

•

The microelectronics evolution

•

SIA Roadmap

•

Semiconductor Manufacturers 2001 Ranking

Metal-oxide-semiconductor

(MOS) and related VLSI technology

•

nMOS

•

pMOS

•

CMOS

•

BiCMOS

•

GaAs

Basic

MOS Transistors

•

Minimum line width

•

Transistor cross section

•

Charge inversion channel

•

Source connected to substrate

•

Enhancement vs. Depletion mode devices

•

pMOS are 2.5 time slower than nMOS due

to electron and hole nobilities

Fabrication

Technology

•

Silicon of extremely high purity

–

chemically purified then grown into

large crystals

•

Wafers

–

crystals are sliced into wafers

–

wafer diameter is currently 150mm,

200mm, 300mm

–

wafer thickness <1mm

–

surface is polished to optical

smoothness

•

Wafer is then ready for processing

•

Each wafer will yield many chips

–

chip die size varies from about 5mmx5mm

to 15mmx15mm

–

A whole wafer is processed at a time

•

Different parts of each die will be made

P-type or N-type (small amount of other atoms intentionally introduced - doping

-implant)

•

Interconnections are made with metal

•

Insulation used is typically SiO2. SiN

is also used. New materials being investigated (low-k dielectrics)

•

nMOS Fabrication

•

CMOS Fabrication

–

p-well process

–

n-well process

•

All the devices on the wafer are made at

the same time

•

After the circuitry has been placed on

the chip

–

the chip is over glassed (with a

passivation layer) to protect it

–

only those areas which connect to the

outside world will be left uncovered (the pads)

•

The wafer finally passes to a test

station

–

test probes send test signal patterns to

the chip and monitor the output of the chip

•

The yield of a process is the

percentage of die which pass this testing

•

The wafer is then scribed and separated

up into the individual chips. These are then packaged

•

Chips are ‘binned’ according to their

performance

CMOS

Technology

•

First proposed in the 1960s. Was not

seriously considered until the severe limitations in power density and

dissipation occurred in NMOS circuits

•

Now the dominant technology in IC

manufacturing

•

Employs both pMOS and nMOS transistors

to form logic elements

•

The advantage of CMOS is that its logic

elements draw significant current only during the transition from one state to

another and very little current between transitions - hence power is conserved.

•

In the case of an inverter, in either

logic state one of the transistors is off. Since the transistors are in series,

(~ no) current flows.

•

See twin-well cross sections

BiCMOS

•

A known deficiency of MOS technology is

its limited load driving capabilities (due to limited current sourcing and

sinking abilities of pMOS and nMOS transistors.

•

Bipolar transistors have

–

higher gain

–

better noise characteristics

–

better high frequency characteristics

•

BiCMOS gates can be an efficient way of

speeding up VLSI circuits

•

See table for comparison between CMOS

and BiCMOS

•

CMOS fabrication process can be extended

for BiCMOS

•

Example Applications

–

CMOS -

Logic

–

BiCMOS -

I/O and driver circuits

–

ECL -

critical high speed parts of the system

Conclusion

•

Design for yield is design for low

cost and quality

•

Traditional techniques are not

sufficient

•

Multiple aspects

•

redundancy

•

defect robustness

•

variation robustness

•

DfY doesn't come for free

•

timing issues

•

wiring congestion increase

•

noise issues

There is a

lot to be gained but also a lot to do!